# Redefining Connectivity: Charting Next-Gen Pathways in Chiplet Interconnects

Tony Chan Carusone, CTO AI Hardware and Edge AI Summit September 11, 2024

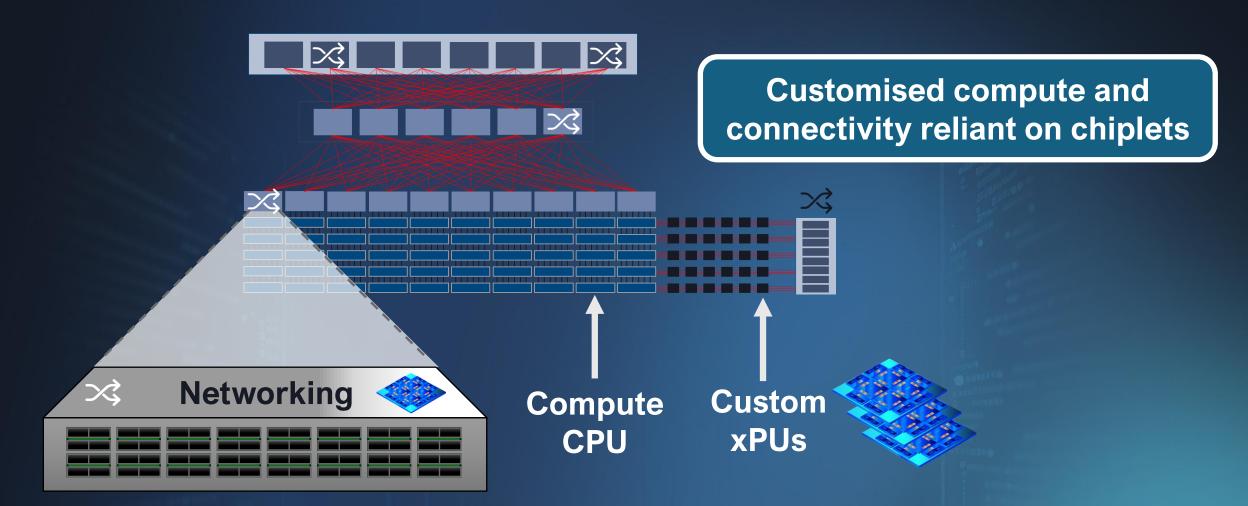

#### **Delivering Custom Silicon in the Data Centre**

#### Outline

• Scaling AI with Connectivity

• The Role of Chiplets for AI Compute

#### • Enabling a Chiplet Ecosystem

# Scaling AI with Connectivity

E ascalar de ascalar de ascalar de accesto

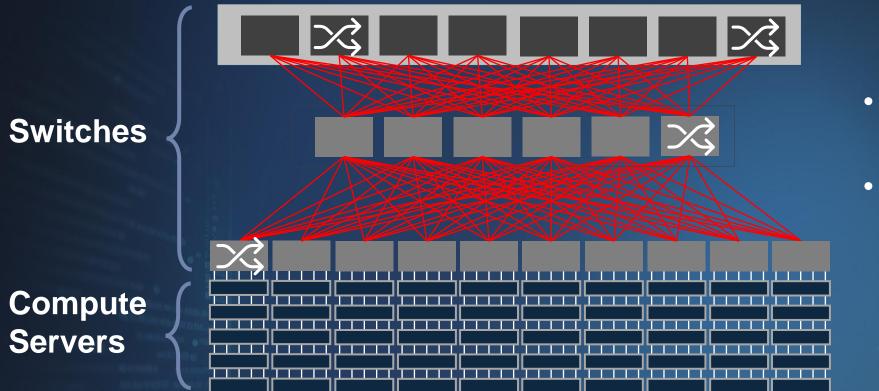

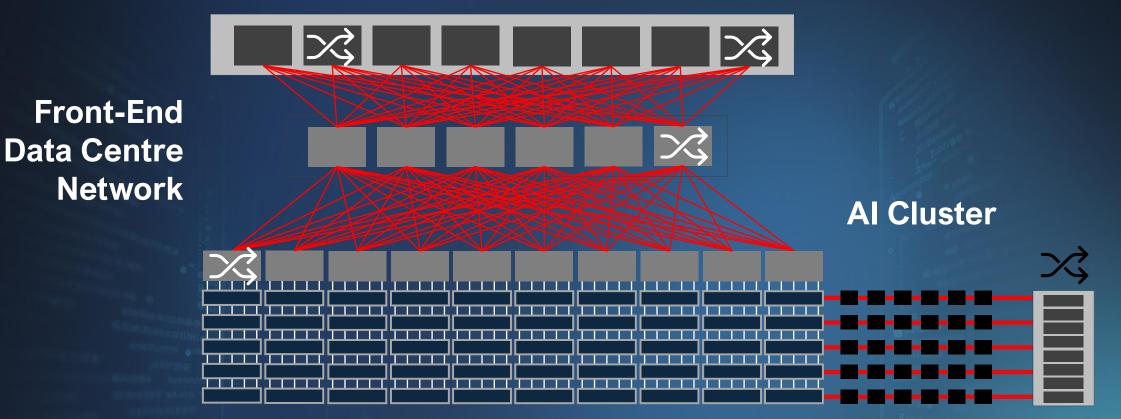

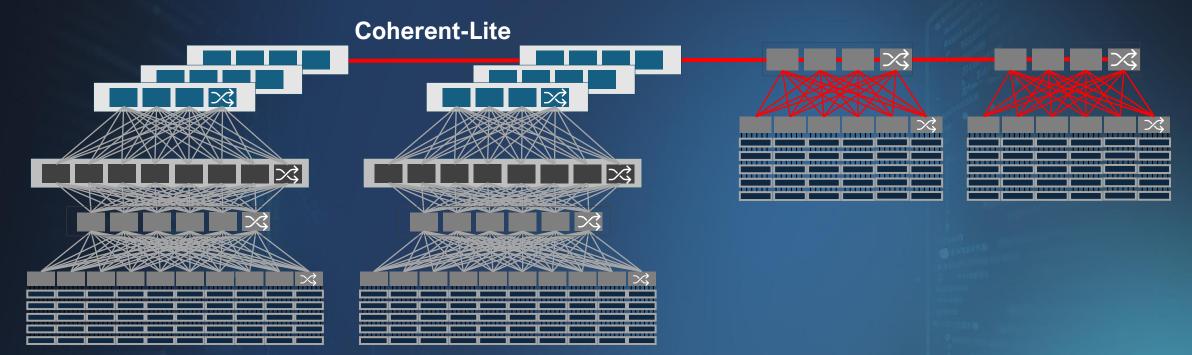

# **Evolving Data Centre Connectivity Landscape**

- Optical and electrical links

- Flexible and redundant networking

This evolution is accelerating and diversifying with AI deployment in the data centre

# Al in the Data Centre – Proliferating Connectivity

# Back-End ML Network Low-latency & high-speed

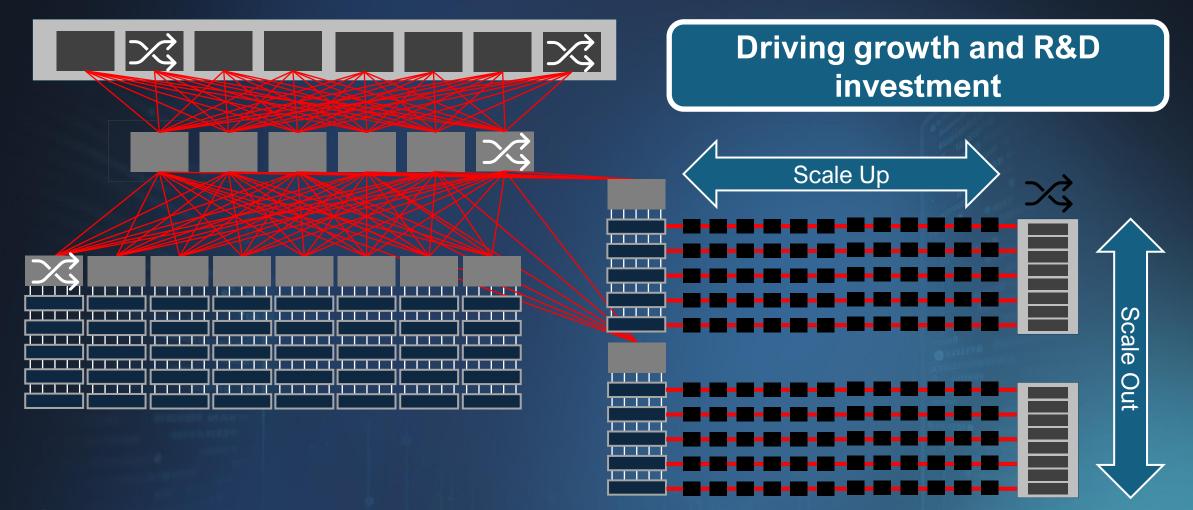

# Scaling Up and Out

#### **Distributed Al**

- Data security & privacy

- Energy efficiency

- Relies heavily on connectivity

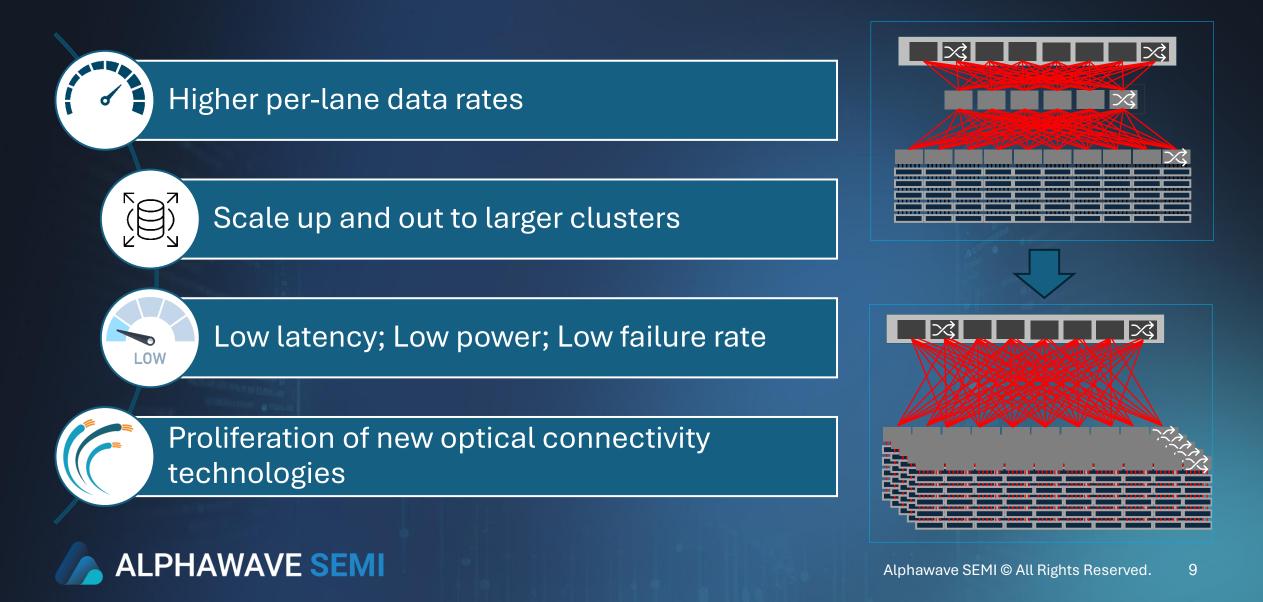

# **Connectivity Demands for Al**

### The Role of Chiplets for AI Compute

ABANA ABARBARA ABARA ABARA

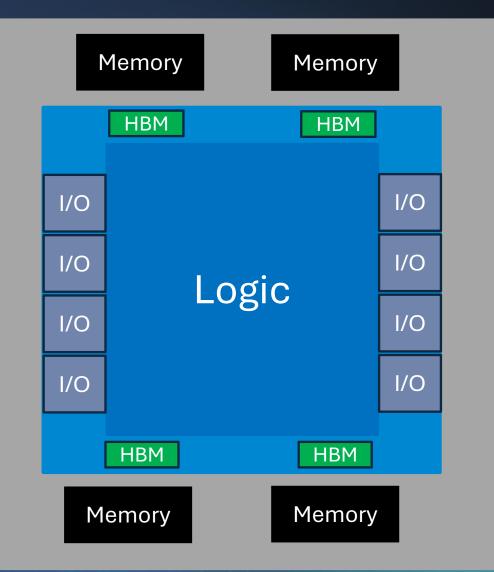

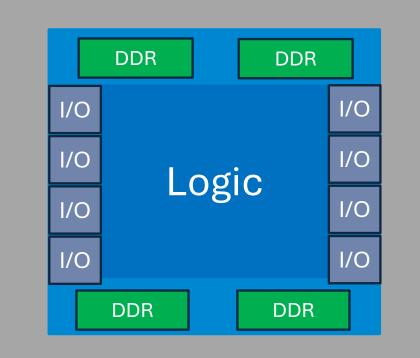

#### **Monolithic Solutions**

#### **Benefits and Drawbacks**

- Requires integration of external IP

- Design and verification time and risk

- Licensing cost

- Maximum size is limited by reticle

- Yield reduced by large die size

- I/O must be in the most advanced technology

- Every I/O must be capable of driving any interconnect

#### **Bandwidth Density**

- Reticle-limited die sizes afford roughly 50mm die edge on the east + west

- 50Tbps aggregate I/O bandwidth requires 1 Tbps/mm

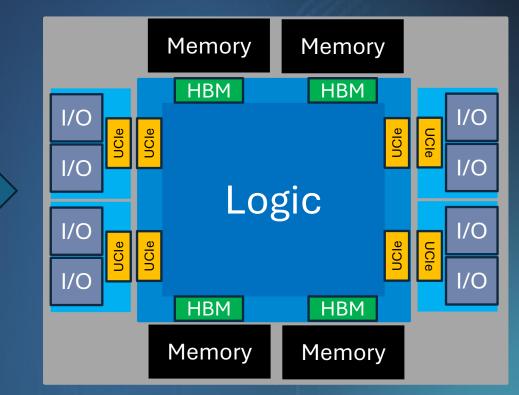

#### Adv. Logic Node

#### **Chiplet-Optimized Node**

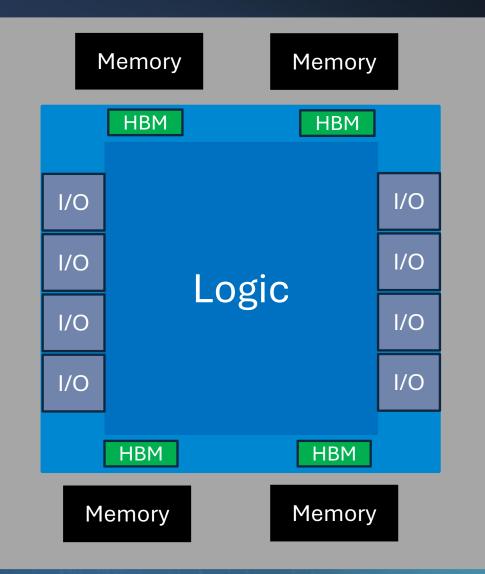

#### Chiplets

- Reduced design time, risk, NRE and silicon costs

- Composability

#### **Chiplet-Optimized Node**

### **Accelerating Hardware Upgrades**

- Reduced design time

- Reduced risk

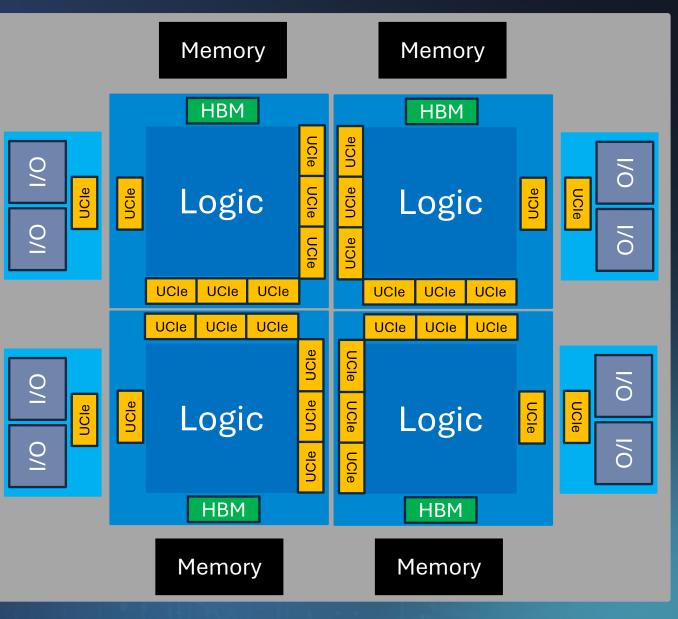

Die-to-Die Interfaces Required for the Chiplet Era

ALPHAWAVE SEMI

Composability

Reduced NRE + Silicon Cost

0/

0

10

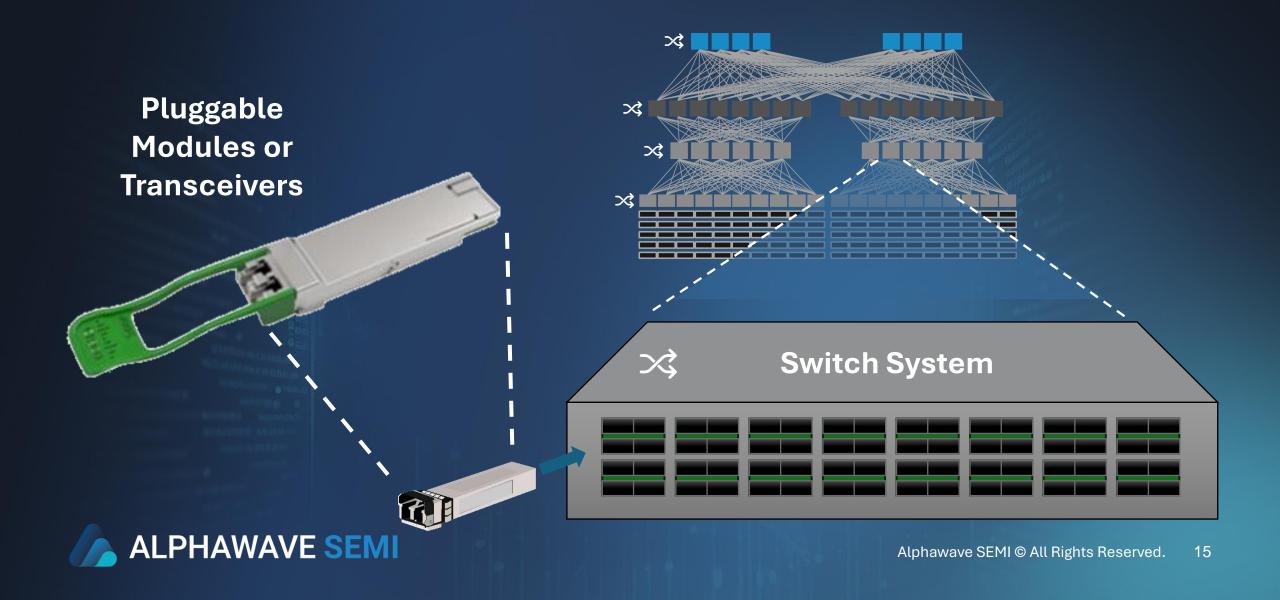

#### **Connectivity Hardware in the Datacenter**

#### **Optical Module Anatomy with Chiplets**

TIAS

Silicon

Laser

Photonics

DRVS

DSP

#### Chiplet devices on a low-cost substrate

**Benefits**:

Power  $\checkmark$ Performance  $\checkmark$ Cost  $\checkmark$

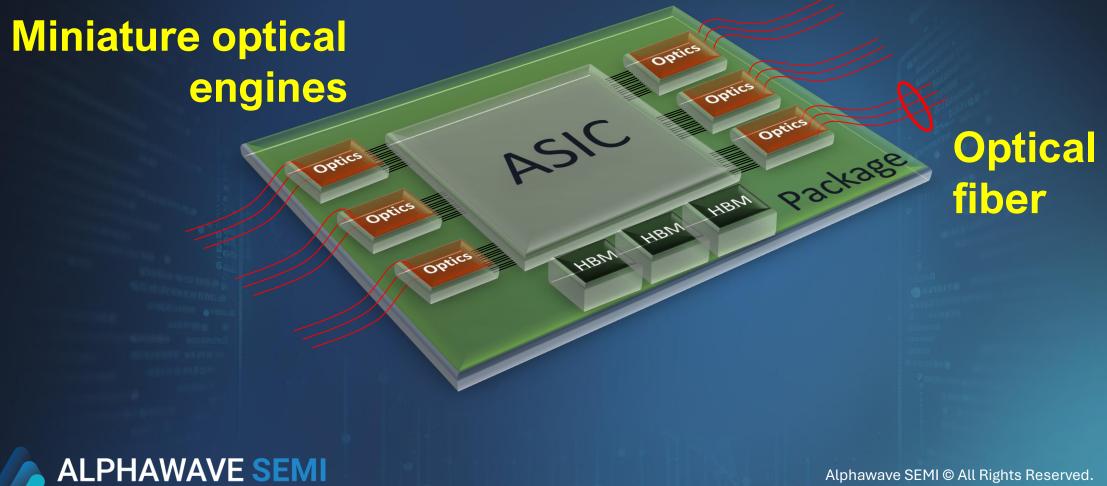

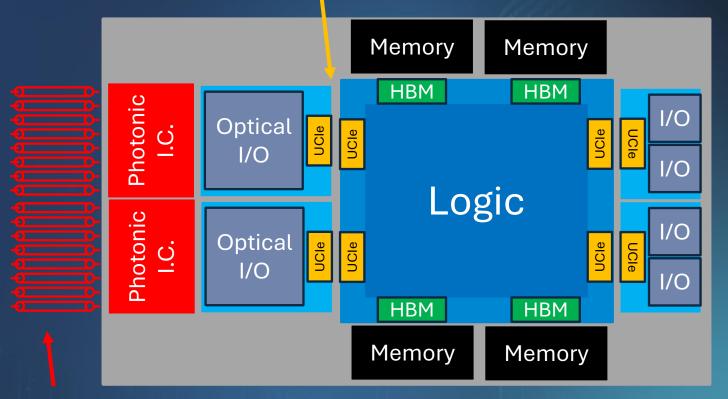

#### **Co-Packaged Optics (CPO)**

# **CPO** Chiplets

- Mix-and-match with electrical I/O chiplets for different applications

- Optical I/O density being pushed by new solutions:

- Multiple wavelengths

- Dense fiber arrays

- Package fan-out

#### Bandwidth ("Beachfront") Density Up to 10 Tbps/mm

Beachfront density can be limited by fiber pitch, optical DSP die area

# Distributed Data Centers Driving New Connectivity

#### Geographically-distributed compute requires broadband connectivity

Future solutions are needed to address these new requirements

# **Enabling the Chiplet Ecosystem**

Autoral Contrational particular particu

# **Design Paradigm Transformation**

#### Monolithic Design with Foundry-Enabled Foundation IP

Accelerated design

Heterogeneous Design with Foundry-Enabled Foundation **Chiplets**

#### Evolution of Hardware Design

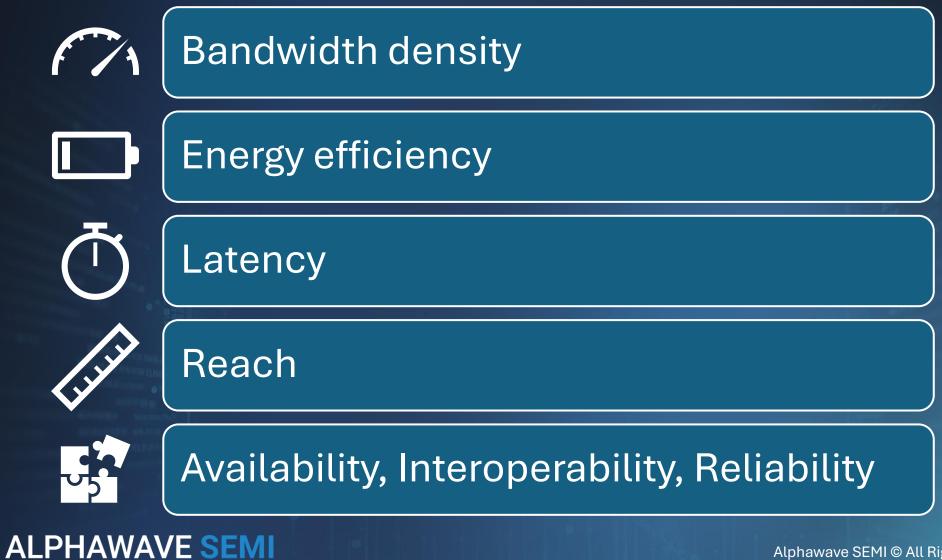

# **Die-to-Die Interfaces Supporting a Chiplet Ecosystem**

# **Key Technologies in Die-to-Die Interfaces**

#### **Signal Integrity**

- Managing Crosstalk

- Interconnect loss compensation

#### **Power Integrity**

- Limited area for supply decoupling

- Variation in packaging technology and dense signal routing complicate power delivery

#### Clocking

- Low-power and low-jitter clock distribution

- Clock/Data alignment

# A Chiplet Portfolio

#### I/O Chiplet

Multi-Standard SerDes IO with Integrated Protocol Controllers: PCIe Gen6 / CXL 3.0 / 112Gbps Ethernet

Compute Chiplet

High Performance, Arm-Based Compute

Memory Expansion Chiplet

Low Latency DDR/HBM

>UCle Die-to-Die Interfaces

#### Takeaways

#### Custom Silicon and Chiplets

#### AI has redefined datacenter infrastructure

- Connectivity technologies are the key to scaling AI clusters and geographically distributed datacenters effectively

- Chiplets enable custom silicon solutions optimized for AI workloads

- Essential to affordably scale performance, achieve lower power, and faster time to market

- A chiplet ecosystem is emerging, enabled by die-to-die interfaces and allowing for a wide variety of chiplet use cases

# **Thank You!**